# DESIGN AND DEVELOPMENT OF IN SITU FPGA-BASED WATER QUALITY MONITORING KIT

BY

# ABDULRAHMAN BAHAA ZAIDAN

A dissertation submitted in fulfilment of the requirement for the degree of Master of Science in Computer and Information Engineering

> Kulliyyah of Engineering International Islamic University Malaysia

> > November 2022

### ABSTRACT

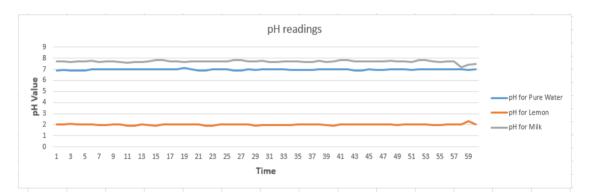

In 2017, about 144 million people collected water from untreated water bodies, such as lakes, streams, and rivers. One of the major causes of death is consuming contaminated or polluted water. Measuring and monitoring water quality are usually done using two methods. The conventional method occurs by taking samples of water and then transferring them to the laboratory. The second method is real-time water quality by integrating the Internet of Things (IoT). This method is preferable as it only requires smart sensors and processors to monitor the water quality. Among the widely used processors are the Arduino and Raspberry Pi. However, these two processors have a limitation, including a limited number of hard-coded input/output pins, unlike the Field Programmable Gate Array (FPGA) processor, which has many input/output pins not hard-coded to allow different interfacing of multiple sensors. Based on the literature, an FPGA platform provides more flexibility and reconfigurability features when compared with the Arduino and Raspberry Pi. This research mainly focuses on designing a reconfigurable multi-core Smart Water Quality System (SWQS) measuring the pH, Total Dissolved Solids (TDS), and turbidity parameters. The hardware design was developed based on the system-on-chip (SoC) design methodology on an FPGA to parallelize the SWQS functionality. A Liquid-Crystal Display (LCD) display has been incorporated into the Raspberry Pi to show real-time data. The Platform Designer on Ouartus II has been used to instantiate four cores to integrate all functions into one processor. The Eclipse tool on Quartus II, on the other hand, was used to program the sensors using embedded C language. The proposed design has been implemented on DE10 Nano FPGA-SoC consuming 9% of logic resources and 57% of internal memory. To verify the proposed system functionality, the sensors were tested on different liquids. To test the pH level, the pH sensor was tested on pure water, lemon juice, and milk to show the acidity and alkalinity. The pH sensor showed 7, less nearly 2, and less than 8 for pure water, lemon juice, and milk, respectively. The TDS sensor successfully detected the salt added to the water, and the TDS values increased to approximately 1800 ppm. Finally, the turbidity sensor revealed the dust inserted in the solution. The more dust in the liquid, the more TDS value there was recorded. Additionally, results showed that the processing time of all the sensors using FPGA is approximately 300 ms for ten readings; on the other hand, the processing time of using other processors, such as Arduino, took 2 s for ten readings. This is because FPGA is functioning at 100 MHz, while Arduino's frequency is not more than 24 MHz. All real-time sensor readings were shown on a Linux Terminal. In conclusion, the proposed FPGA-based system can be utilized as a heterogeneous multi-core system for many applications, including the SWQS.

## ملخص البحث

اكثر من مائة واربع واربعون مليون انسان ياخذون احتياجاتهم من المياه من مصادر غير معالجة مثل الانحار والبحيرات .في بعض الدول النامية ,معظم المصانع تقوم برمي الفضلات في المياه وهذا يجعل المياه بالقرب من المصانع اكثر تلوثا لأنها تحمل مواد كيميائيه بالأضافه إلى المواد الثقيلة .هذه المواد تؤثر بشكل سلبي على البيئة وعلى الكائنات الحية التي تعيش في المياه لان المواد الثقيلة تنشر الفايروسات والبكتيريا .في هذه الايام يتم قياس جودة المياه بطريقتين هما اما الطريقة التقليدية وهي عبارة عن اخذ عينات من المياه ونقلها الى المختبر ومن ثم قياس جودتما ,ولكن هذه الطريقة تحتاج الى وقت وتكلفه اكثر .بالاضافة الى ذلك , حالة المياه من الممكن ان تتغير خلال عملية النقل .اما الطريقة الثانية فهي قياس جودة المياه بأستخدام الحساسات الذكية مع المعالجات ونقل البيانات بطرق مختلفة .هذه الطريقة مفضلة بشكل أكبر من الطريقة التقليدية لانها فقط تحتاج إلى الحساسات الذكية بالاضافة إلى المعالج لقياس جودة المياه في كل وقت . هذه الطريقة ستساعد المستخدم على اتخاذ القرار بسرعة في الحالات المفاجأة .لهذا فأن هذا المشروع يركز بشكل اساسى على استخدام حساسات لقياس الأس الهيدروجيني والعكورة بالأضافة الى كمية المواد الذائبة .بعد ذلك تقوم مصفوفة البوابات المنطقية القابلة للبرمجة بمعالجة البيانات وارسالها لأجل عرضها على الشاشة .هذا المشروع سيقلل من تعقيد الأجهزة الأخرى المستخدمة في قياس جودة المياه .وسوف تقوم بأستخدام الأجهزة مع البرمجة لتقليل الوقت المستخدم في تطوير جهاز متحسس المياه الذكي .اخيرا وليس اخرا ,جهاز الراسبري باي سيستخدم فقط لعرض البيانات على الشاشة المتربطة به .سيقوم معالج الراسبري باي بأستلام البيانات عن طريق تطبيق مبرمج بداخله ومن ثم عرضها على الشاشة .الجهاز المصمم قدتم اختباره على سوائل مختلفة مثل المياه النقية ,عصير الليمون ,الحليب لقياس الأس الهيدروجيني .

اما نسبة العكورة فقد تم استخدام المياه النقيه بالاضافه الى مياه مع القليل من الرواسب ومياه مع الكثير من الرواسب. اخيرا فقد تم استخدام المياه النقية ومياه تحتوي على الملح لقياس المواد المذابة في الماء. عن طريق هذا المشروع يمكن استخدام البيانات عن طريق ربطها ببرامج اتخاذ القرار, تحليل البيانات وغيرها من البرامج.

## **APPROVAL PAGE**

I certify that I have supervised and read this study and that, in my opinion, it conforms to acceptable standards of scholarly presentation and is fully adequate, in scope and quality, as a dissertation for the degree of Master of Science Engineering.

Binti Azman Ameli Super

Huda Adibah Mohd Ramli Co-Supervisor

I certify that I have read this study and that, in my opinion, it conforms to acceptable standards of scholarly presentation and is fully adequate, in scope and quality, as a dissertation for the degree of Master of Science Engineering..

| 100011111 | azuin Ab.<br>Examine | <br> | • • • • • |

|-----------|----------------------|------|-----------|

|           |                      |      |           |

Suriza Ahmad Zabidi Internal Examiner

This dissertation was submitted to the Department of Electrical and Computer Information and is accepted as a fulfilment of the requirement the degree of Master of Science Engineering.

> Rafiqul Islam Head, Department of Electrical and Computer Information Engineering

This dissertation was submitted to the Kulliyyah of Engineering and is accepted as a fulfilment of the requirement for the degree of Master of Science Engineering.

Sany Izan Ihsan Dean, Kulliyyah of Engineering

## DECLARATION

I hereby declare that this dissertation is the result of my investigations, except where otherwise stated. I also declare that it has not been previously or concurrently submitted as a whole for any other degrees at IIUM or other institutions.

Abdulrahman Bahaa Zaidan

| fra       |

|-----------|

| Signature |

Date 2022/12/05

## INTERNATIONAL ISLAMIC UNIVERSITY MALAYSIA

## DECLARATION OF COPYRIGHT AND AFFIRMATION OF FAIR USE OF UNPUBLISHED RESEARCH

## DESIGN AND DEVELOPMENT OF IN SITU WATER QUALITY KIT

I declare that the copyright holders of this dissertation are jointly owned by the Student and IIUM.

Copyright © 2022 Abdulrahman Bahaa Zaidan and International Islamic University Malaysia. All rights reserved.

No part of this unpublished research may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise without prior written permission of the copyright holder except as provided below

- 1. Any material contained in or derived from this unpublished research may only be used by others in their writing with due acknowledgement.

- 2. IIUM or its library will have the right to make and transmit copies (print or electronic) for institutional and academic purposes.

- 3. The IIUM library will have the right to make, store in a retrieval system and supply copies of this unpublished research if requested by other universities and research libraries.

By signing this form, I acknowledged that I have read and understand the IIUM Intellectual Property Right and Commercialisation policy.

Affirmed by Abdulrahman Bahaa Zaidan

2022/12/05

Signature

Date

## ACKNOWLEDGEMENTS

First and foremost, I would like to thank Allah for blessing me each and every day. Thanks for the strength, wisdom, and faith to make it through life's everyday challenges.

I would like to thank my parents. There are so many things that I want to thank them for. They are the reason behind all of my success, and I am forever indebted to them. I would especially like to thank Associate Professor Amelia Wong Binti Azman for her outstanding guidance, advice, inspiration, and encouragement throughout my research progress. It is my greatest honor to work under her supervision. Thank you for nurturing me into a hard-working student and for all your patience and guidance. You were more than just supervisors to me. I am deeply indebted to you.

In addition, my gratitude goes to my beloved, lovely wife; for her prayers, understanding, and endurance while away.

Finally, I want to thank Fawaz Mohammed for his countless midnight calls and messages just to do this research; I am so grateful and thankful to you. I am very thankful for all of the above for being the solid support system in my life. Thank you. Allah blesses you

Once again, we glorify Allah for His endless mercy on us, one of which is enabling us to successfully round off the efforts of writing this thesis. Alhamdulillah.

# TABLE OF CONTENTS

| Abstract                                                | ii   |

|---------------------------------------------------------|------|

| Abstract in Arabic                                      | iii  |

| Approval Page                                           | v    |

| Declaration                                             | vi   |

| Copyright Page                                          | vii  |

| Acknowledgements                                        | viii |

| Table of Contents                                       | ix   |

| List of Tables                                          | xii  |

| List of Figures                                         | xiii |

|                                                         |      |

| CHAPTER ONE: INTRODUCTION                               |      |

| 1.1 Overview                                            |      |

| 1.2 Research Background                                 |      |

| 1.2.1 Field Programmable Gate Array (FPGA)              |      |

| 1.2.2 Heterogeneous System Architecture (HSA)           |      |

| 1.3 Problem Statement                                   |      |

| 1.4 Research Objectives                                 |      |

| 1.5 Research Scope                                      |      |

| 1.6 Dissertation Layout                                 |      |

| 1.7 Summary                                             | 7    |

|                                                         |      |

| CHAPTER TWO: LITERATURE REVIEW                          |      |

| 2.1 Overview                                            |      |

| 2.2 Different Water Quality Approaches                  |      |

| 2.2.1 Conventional Approach                             |      |

| 2.2.2 Internet of Things (IoT) Approach                 |      |

| 2.3 Sensors Used in Monitoring Water Quality Parameters |      |

| 2.3.1 pH Sensor                                         |      |

| 2.3.2 Temperature Sensor                                |      |

| 2.3.3 Turbidity Sensor                                  |      |

| 2.3.4 Conductivity Sensor                               | 14   |

| 2.3.5 Dissolved Oxygen Sensor                           |      |

| 2.3.6 Total Dissolved Solids (TDS) Sensor               | 16   |

| 2.3.7 Free Chlorine Sensor                              | 16   |

| 2.3.8 Water Level Sensor                                |      |

| 2.4 Related Research                                    |      |

| 2.4.1 Arduino as a Processing Platform                  |      |

| 2.4.2 Raspberry Pi as Processing Platform               | 26   |

| 2.4.3 TI CC3200 as Processing Platform                  | 30   |

| 2.4.3.1 FPGA as Processing Platform                     |      |

| 2.4.4 Other Processing Platforms                        |      |

| 2.4.5 Summary of Related Works                          |      |

| 2.5 Proposed FPGA-Based SWQS                            |      |

| 2.6 Understanding The FPGA-SoC Heterogeneous system     |      |

| 2.6.1 FPGA Chip                                         |      |

| 2.6.2 System-on-Chip                                    | 45   |

| 2.6.3 Heterogeneous Platform                                | 45 |

|-------------------------------------------------------------|----|

| 2.6.4 Features of FPGA-SoC Heterogeneous Platform           |    |

| 2.6.5 Memory Management on FPGA-SoC                         |    |

| 2.6.6 Quartus II Development Software                       |    |

| 2.6.7 Quartus Intellectual Property Libraries               |    |

| 2.6.8 Linux Terminal Interface                              |    |

| 2.6.8.1 Linux Kernel Compilation                            |    |

| 2.7 Summary                                                 |    |

|                                                             |    |

| CHAPTER THREE: METHODOLOGY                                  |    |

| 3.1 Overview                                                |    |

| 3.2 Research Methodology                                    |    |

| 3.3 Proposed Design Development and System Requirement      |    |

| 3.3.1 Smart Water Quality System (SWQS)                     |    |

| 3.3.1.1 Interfacing Multiple Sensors                        |    |

| 3.4 SWQS Hardware Design                                    |    |

| 3.5 SWQS Software Design                                    |    |

| 3.6 Proposed Design Power Cycle                             |    |

| 3.7 Proposed Design Testing Plan                            |    |

| 3.8 The Design Cycle of The Proposed FPGA-Based SWQS        |    |

| 3.8.1 The Hardware Design Flow of SWQS                      | 70 |

| 3.8.1.1 Processors                                          |    |

| 3.8.1.2 Memory                                              | 73 |

| 3.8.1.3 Clocking and Synchronization                        | 73 |

| 3.8.1.4 Data Transfer Protocols                             | 74 |

| 3.8.1.5 System Peripherals                                  | 75 |

| 3.8.1.6 Bridges                                             | 78 |

| 3.8.1.7 Pin Assignment                                      | 79 |

| 3.8.1.8 Synthesis Report                                    |    |

| 3.8.2 The Software Design Flow of SWQS                      |    |

| 3.8.2.1 Firmware Development Flow                           |    |

| 3.8.2.2 The Linux Application Development Flow of           |    |

| SWQS                                                        |    |

| 3.9 The Embedded Linux Design Flow of SWQS                  |    |

| 3.9.1 Bootloader Compilation                                |    |

| 3.9.2 Root File-system Creation                             |    |

| 3.10 Adding New Core to SWQS Design                         |    |

| 3.11 Summary                                                |    |

| CHAPTER FOUR: RESULT AND ANALYSIS                           | 89 |

| 4.1 Introduction                                            |    |

| 4.2 Results                                                 |    |

| 4.2.1 The Results of the Quartus Project Compilation        |    |

| 4.2.2 The Implementation of Prototype                       |    |

| 4.2.3 Design Verification Method                            |    |

| 4.2.4 The Results of the SWQS Linux-Based Application       |    |

| 4.3 Discussion                                              |    |

| 4.3 Discussion<br>4.3.1 Motivations of the Middleware Layer |    |

| 4.3.2 System Flexibility                                    |    |

| 4.3.3 Applications of the Design                            |    |

| +.3.3 Applications of the Design                            |    |

| 4.4 SWQS Design Compared to Previous Work |  |

|-------------------------------------------|--|

| 4.5 Summary                               |  |

| CHAPTER FIVE: CONCLUSION AND FUTURE WORK  |  |

| 5.1 Conclusion                            |  |

| 5.2 Future Work                           |  |

| REFERENCES                                |  |

## LIST OF TABLES

| Table 2.1 | Summary Table                                                | 38 |

|-----------|--------------------------------------------------------------|----|

| Table 2.2 | Summary of All Sensors Used in Each Study Given in Table 2.1 | 43 |

| Table 2.3 | Files Generated After the Yocto Compilation                  | 54 |

## LIST OF FIGURES

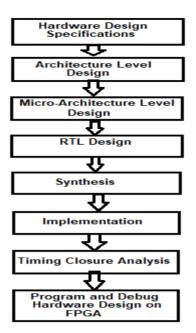

| Figure 1.1  | Hardware Design Flow of FPGA (Intel, 2020)                     | 3  |

|-------------|----------------------------------------------------------------|----|

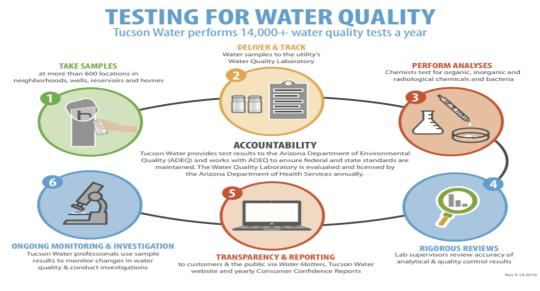

| Figure 2.1  | Conventional-Based Water Quality Monitoring Example            |    |

|             | (Tucsonaz, 2015)                                               | 10 |

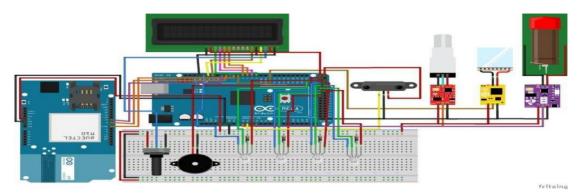

| Figure 2.2  | IoT-Based Water Quality Monitoring Example Using Arduino       |    |

|             | (Pinterest, 2017)                                              | 11 |

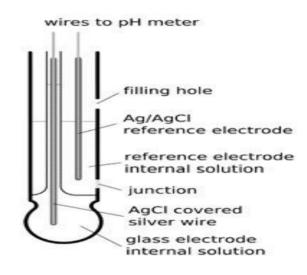

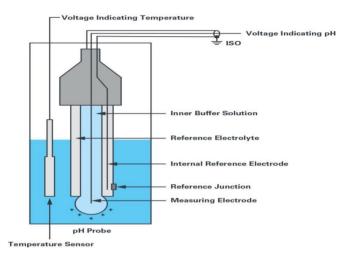

| Figure 2.3  | Configuration of pH Probe (Aaruththiran, Yujia, & Bagherian,   |    |

|             | 2019)                                                          | 12 |

| Figure 2.4  | Configuration of Temperature Probe (Dhaker, 2020)              | 13 |

| Figure 2.5  | Turbidity Sensor                                               | 14 |

| Figure 2.6  | Electrical Conductivity Sensor                                 | 15 |

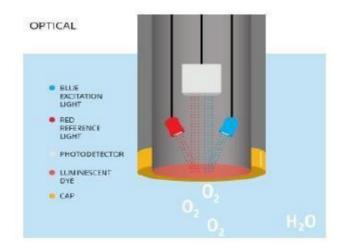

| Figure 2.7  | Dissolved Oxygen Optical Sensor (Staff, 2020)                  | 15 |

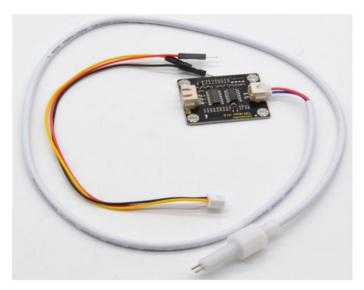

| Figure 2.8  | Total Dissolved Solids Sensor                                  | 16 |

| Figure 2.9  | Free Chlorine Sensor (Karak et al., 2012).                     | 17 |

| Figure 2.10 | Ultrasonic Level Sensor for Liquids                            | 18 |

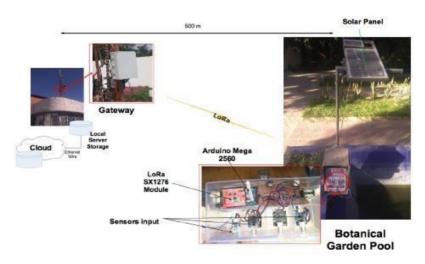

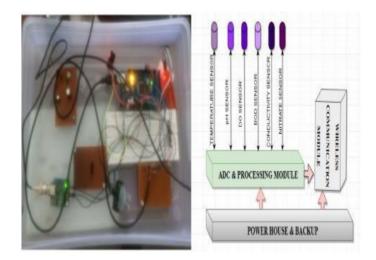

| Figure 2.11 | Overall Water Quality Monitoring System (Ngom et al., 2019)    | 19 |

| Figure 2.12 | Prototype of Water Quality Monitoring System (Li et al., 2018) | 20 |

| Figure 2.13 | Overall Water Quality Scheme (Chowdury et al., 2019)           | 21 |

| Figure 2.14 | Overall System Architecture (Lezzar et al., 2020)              | 22 |

| Figure 2.15 | Hardware Implementation for Water Quality Monitoring Device    |    |

|             | in Pipeline (Saravanan et al., 2018)                           | 23 |

| Figure 2.16 | Experimental Setup of SQWM System (Mukta, Islam, Barman,       |    |

|             | Reza, & Khan, 2019)                                            | 24 |

| Figure 2.17 | Circuit and Block Diagram of IoT System (Pujar et al., 2020)   | 25 |

| Figure 2.18 | System General Blocks and Data Flow (Encinas et al., 2017)     | 26 |

| Figure 2.19 | Block Diagram of Developed (Khatri et al., 2020)               | 27 |

| Figure 2.20 | IoT-based Monitoring System (Niswar et al., 2018)              | 28 |

| Figure 2.21 | System Architecture (Raju & Varma, 2017)                       | 29 |

| Figure 2.22 | Overall Block Diagram (Vijayakumar & Ramya, 2015)              | 30 |

| Figure 2.23 | Overall Block Diagram (Geetha & Gouthami, 2016)                | 32 |

| Figure 2.24 | Overall Block Diagram (Billah et al., 2019)                    | 33 |

| Figure 2.25 | The Block Diagram of Smart Water Quality Monitoring System   |    |

|-------------|--------------------------------------------------------------|----|

|             | (Myint et al., 2017)                                         | 34 |

| Figure 2.26 | Block Diagram of Proposed System (Birje et al., 2016)        | 35 |

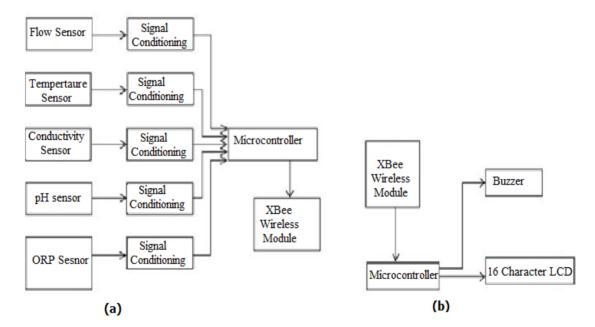

| Figure 2.27 | (a) Module 1: The Measurement and Sensing Module Block       |    |

|             | Diagram (b) Module 2: The Notification Module Block          |    |

|             | Diagram (Cloete et al., 2016)                                | 36 |

| Figure 2.28 | Architecture of the E-Sensor AQUA System (Danh et al., 2020) | 37 |

| Figure 2.29 | Cyclone V SoC FPGA from Intel (Intel PSG Website, 2020).     | 45 |

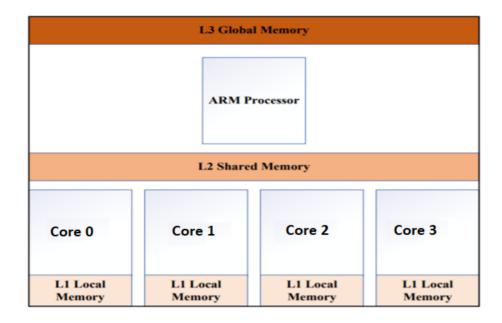

| Figure 2.30 | Example of a Memory Model of the Proposed SWQS Design        | 48 |

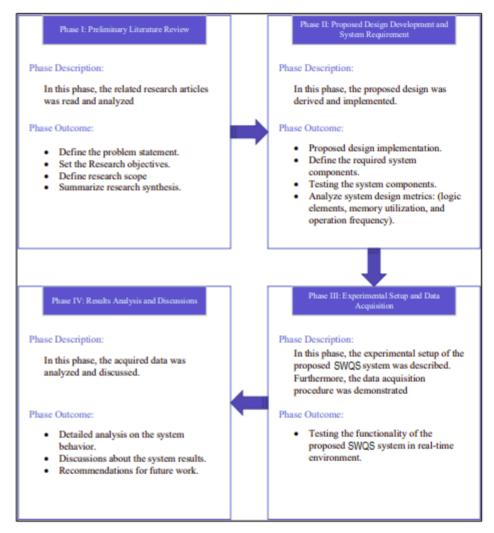

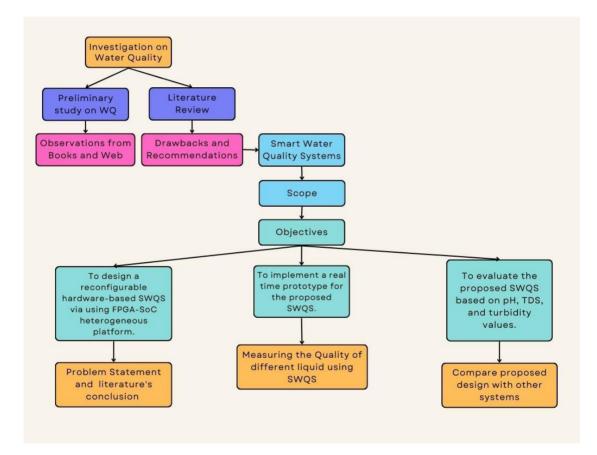

| Figure 3.1  | Research Methodology Phases                                  | 57 |

| Figure 3.2  | Research Methodology of the Proposed SWQS                    | 58 |

| Figure 3.3  | Overall methodology of the Proposed SWQS                     | 60 |

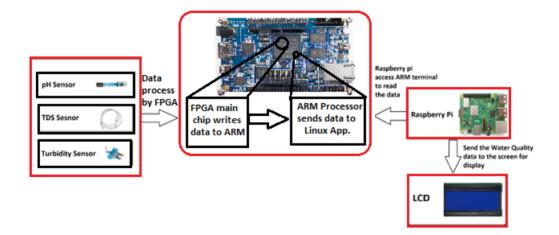

| Figure 3.4  | Proposed System Blocks and Data Flow                         | 61 |

| Figure 3.5  | Multi-Core Heterogeneous System Architecture Design of the   |    |

|             | Proposed Design                                              | 62 |

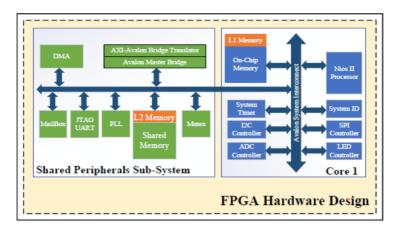

| Figure 3.6  | FPGA Single Core Processing Element of the Proposed Design   | 63 |

| Figure 3.7  | Proposed SWQS Hardware Proposed Data Acquisition Design      | 64 |

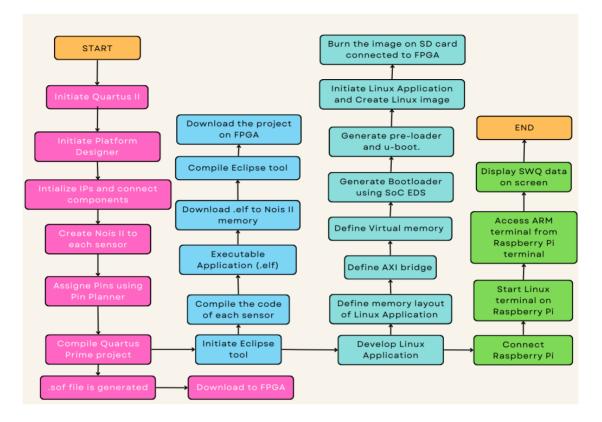

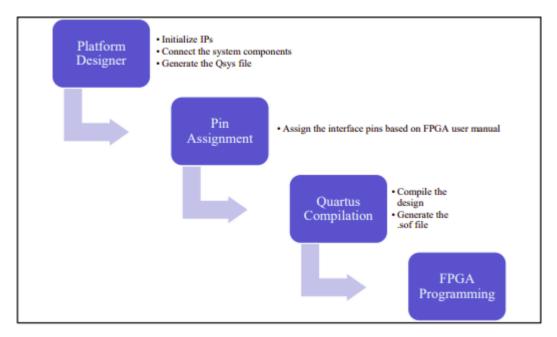

| Figure 3.8  | The Summary of the FPGA Hardware Design Flow                 | 65 |

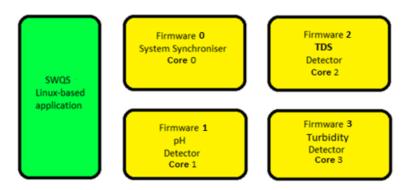

| Figure 3.9  | Firmware Applications for Each Core with SWQS Linux-based    |    |

|             | Application                                                  | 65 |

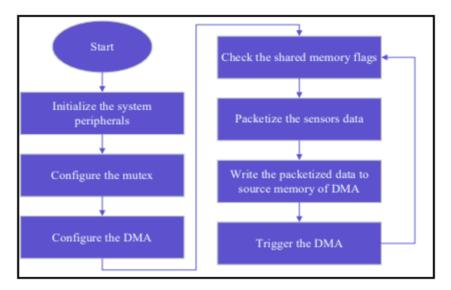

| Figure 3.10 | Flow Diagram of Firmware 0                                   | 66 |

| Figure 3.11 | The Sensor's Core Firmware Flow Diagram                      | 67 |

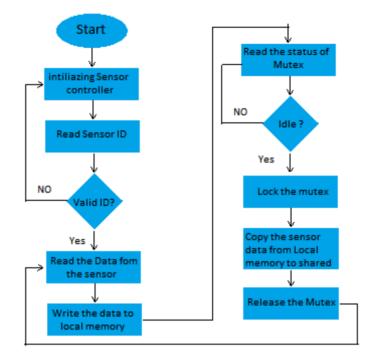

| Figure 3.12 | The Proposed Design Abstraction Layers                       | 68 |

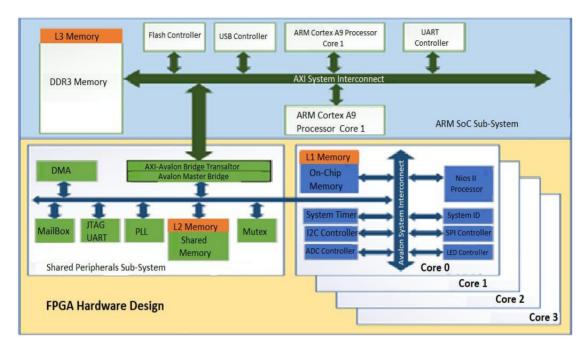

| Figure 3.13 | The Architecture of the Proposed SWQS                        | 71 |

| Figure 3.14 | The Configuration of the ARM Processor                       | 72 |

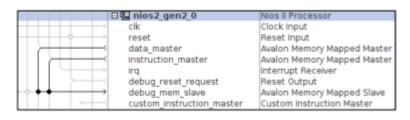

| Figure 3.15 | Nios II Processor Configuration                              | 72 |

| Figure 3.16 | The Configuration of On-chip-Memory Controller               | 73 |

| Figure 3.17 | Clock source IP in Platform Designer                         | 73 |

| Figure 3.18 | PPL Configuration in Platform Designer                       | 74 |

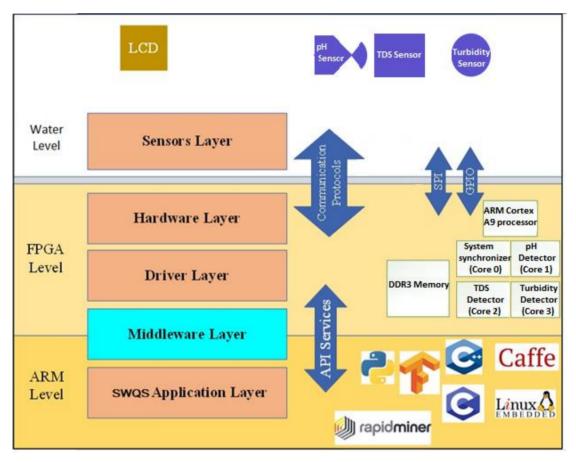

| Figure 3.19 | ADC Input Signals                                            | 75 |

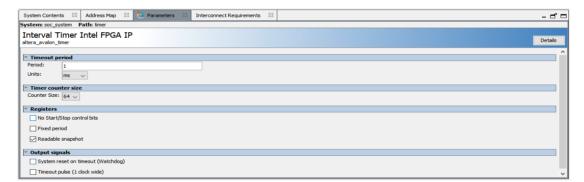

| Figure 3.20 | System Timer IP Configurations in Platform Designer          | 75 |

| Figure 3.21 | mSGDMA Controller IP Configurations                          | 76 |

| Figure 3.22 | Mutex configuration in Platform Designer                     | 76 |

| Figure 3.23 | The Configuration of JTAG IP in Platform Designer            | 77 |

| Figure 3.24 | The Configuration of System ID Core in Platform Designer        | 77  |

|-------------|-----------------------------------------------------------------|-----|

| Figure 3.25 | Avalon Memory Mapped Controller IP                              | 78  |

| Figure 3.26 | Address Span Extender IP                                        | 79  |

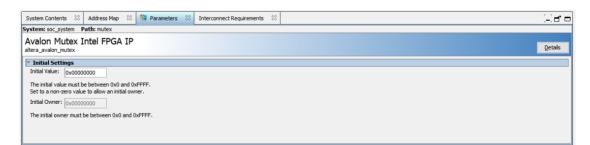

| Figure 3.27 | Top View of Pin Assignment                                      | 80  |

| Figure 3.28 | Synthesis Report of the Design                                  | 81  |

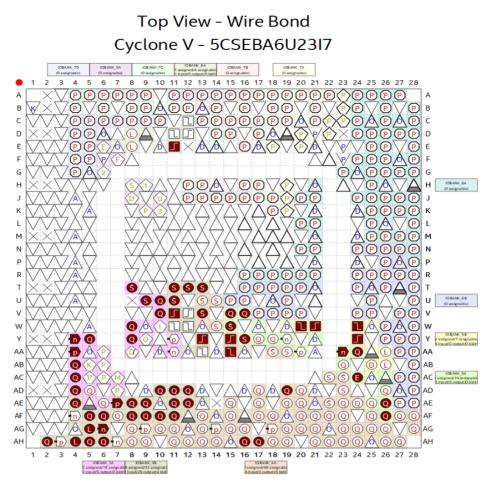

| Figure 3.29 | Nios II Software Development Flow                               | 82  |

| Figure 3.30 | The Entire FPGA Development Flow                                | 83  |

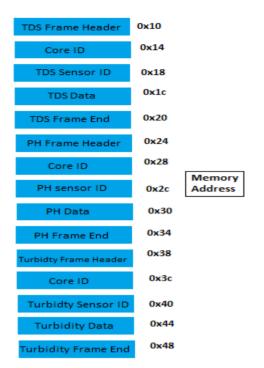

| Figure 3.31 | SWQS Application Memory Layout                                  | 84  |

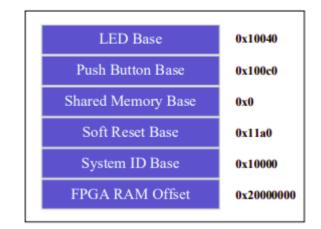

| Figure 3.32 | FPGA Components Base Addresses                                  | 85  |

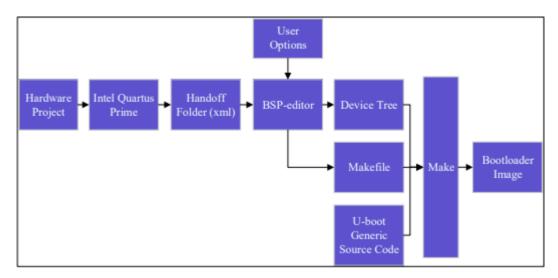

| Figure 3.33 | U-Boot Development Flow                                         | 87  |

| Figure 3.34 | Nios II Core Connections                                        | 87  |

| Figure 4.1  | The Result of the System Compilation                            | 90  |

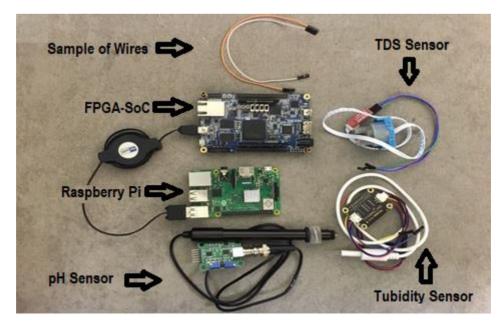

| Figure 4.2  | System Setup Components                                         | 90  |

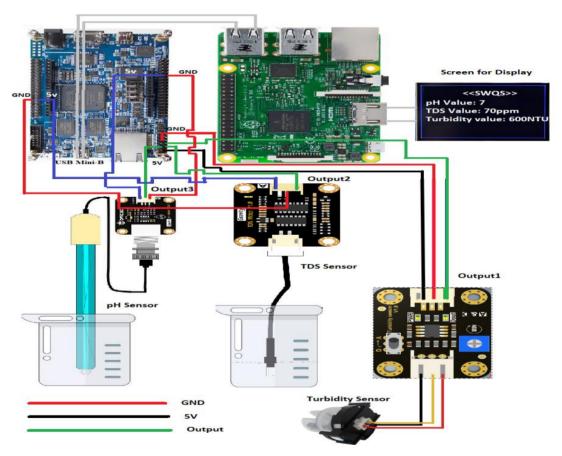

| Figure 4.3  | Design Block Diagram                                            | 91  |

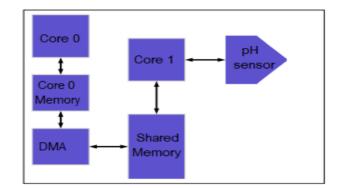

| Figure 4.4  | Core 1 pH Data Collection and Data Transfer Test Block          |     |

|             | Diagram                                                         | 93  |

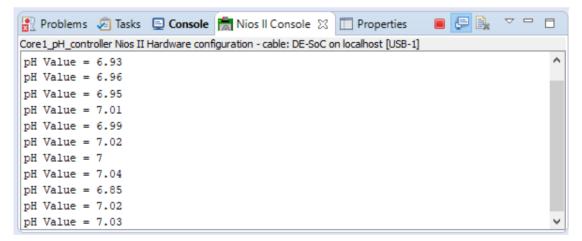

| Figure 4.5  | Readings of pH Sensor                                           | 93  |

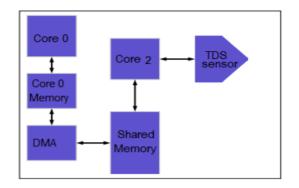

| Figure 4.6  | The Block Diagram of Core 2 TDS Data Collection and Data        |     |

|             | Transfer Test                                                   | 94  |

| Figure 4.7  | Readings of TDS Sensor                                          | 94  |

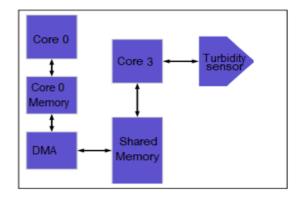

| Figure 4.8  | The Block Diagram of Core 3 Turbidity Data Collection and       |     |

|             | Data Transfer Test                                              | 95  |

| Figure 4.9  | Readings of Turbidity Sensor                                    | 95  |

| Figure 4.10 | Line Graph of pH Values of Pure Water, Lemon Juice, and Milk    | 96  |

| Figure 4.11 | Testing the pH Sensor                                           | 96  |

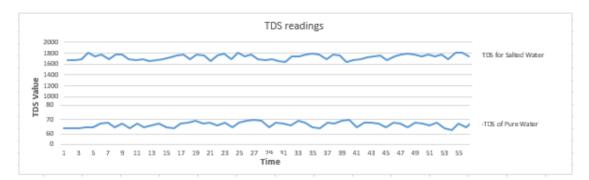

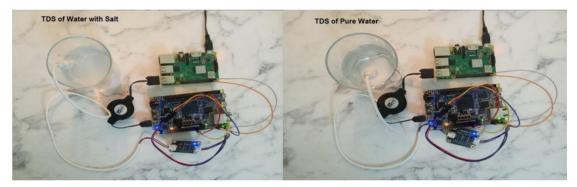

| Figure 4.12 | Line graph of TDS Values of Pure Water and Water with Salt      | 97  |

| Figure 4.13 | Testing of the TDS Sensor                                       | 97  |

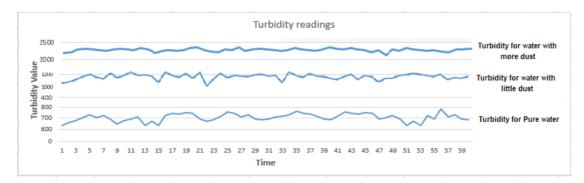

| Figure 4.14 | Line graph of Turbidity Values of Pure Water, Water with Little |     |

|             | Dust, and Water with More Dust                                  | 98  |

| Figure 4.15 | Testing the Turbidity Sensor                                    | 98  |

| Figure 4.16 | SWQS Results on Linux-Based Application                         | 99  |

| Figure 4.17 | SWQS Proposed Single Design Core                                | 101 |

### **CHAPTER ONE**

## INTRODUCTION

#### **1.1 OVERVIEW**

Water quality is an important factor that needs to be considered as it is directly related to people's lives. Therefore, this research focuses on designing a Smart Water Quality System (SWQS) Field Programmable Gate Array (FPGA)-based to eliminate the problems and drawbacks of previous works. This chapter illustrates the work by giving a brief background and defining the research problem. The chapter then presents the research motivation. Finally, it emphasizes the research scope.

Section 1.3 defines the research problem statement. Then, in Sections 1.4 and 1.5, the research objectives and research scope are presented, respectively. In addition, an outline of the main structure of the thesis is briefly reported in Section 1.6. Finally, Section 1.7 summarizes Chapter 1.

#### **1.2 RESEARCH BACKGROUND**

One of the major causes of death is consuming contaminated or polluted water. According to the World Health Organization (WHO), in 2017, 2.2 billion people were drinking water without any safety management services, and 144 million collected water from untreated water bodies, such as lakes, streams, and rivers ("2.1 Billion People Lack Safe Drinking Water at Home, More than Twice as Many Lack Safe Sanitation," 2017). To reduce the death rate due to contaminated and polluted water, measuring water quality, especially for consumption, becomes important. Water quality indicators can mean differently. It shows the suitability of any water body used for different uses, such as drinking, cooking, and cleaning. Water usage has different chemical, biological, and physical acceptance levels. For instance, drinking water has specified water quality parameters, such as pH levels ranging from 6.5 to 8.5. As many parameters need to be measured, thus, several sensors must be employed for the water quality test. To this date, the water safety management services that utilize a system that support large computational loads need a huge amount of power, not portable, and big devices, making it impossible to be commercialized.

Hence, it is pertinent to establish a new smart system considering the latest technological advancement that can carry out the huge computational load at lower power but with high performance. Therefore, this research proposes a water quality system that utilizes the FPGA platform and the Adcanced RISC Machine (ARM) processor.

#### **1.2.1 Field Programmable Gate Array (FPGA)**

FPGA is a reconfigurable computing device with several programmable units that could solve any computational issues (Giesemann, Paya-Vaya, Blume, Limmer, & Ritter, 2014). This device is an integrated circuit made of semiconductor material, and the main feature of FPGA is the device's electrical functionality can be reconfigured even by the customer. As a result, these powerful devices can be customized to accelerate key workloads and enable design engineers to adapt to emerging standards or changing requirements.

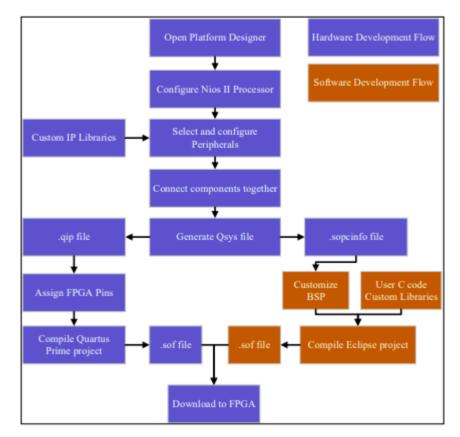

Figure 1.1 illustrates the common design flow for an FPGA platform, beginning with hardware design specifications. The hardware design specifications consist of the needed hardware design's functionality, memory size, the number of input/output ports, speed, and finally, how the data transfers. The next step is the architecture design, in which the hardware design can be further split into system and sub-system modules, i.e., the micro-architecture level design (Gerstlauer et al., 2009).

Figure 1.1 Hardware Design Flow of FPGA (Intel, 2020)

Once the architecture and the micro-architecture level of the needed hardware design are completed, the Register Transfer Level (RTL) will begin. At this level, Hardware Description Language (HDL) will be used to translate the system and subsystem blocks into a Hardware netlist ("AN 311: Standard Cell ASIC to FPGA Design Methodology and Guidelines," 2009). Synthesis and implementation processes will begin when the digital module design is done. These two steps will translate the HDL design into a physical netlist prepared for timing analysis. Timing analysis is the process of ensuring the hardware design is working from a time perspective. In other words, it will check whether the design is the speed requirements of the system or not (Gerstlauer et al., 2009). In the end, the hardware design will be executed on an FPGA board.

#### **1.2.2 Heterogeneous System Architecture (HSA)**

A Heterogeneous System Architecture (HSA) is a computer platform that functions with associated software that makes different kinds of processors with different architectures work in shared memory efficiently and cooperatively from a single source program (Kyriazis, 2012). Integrating multiple computing elements at low frequencies leads to high performance with low power consumption; architectural heterogeneity improves platform flexibility (Burgio et al., 2016). This heterogeneous platform, such as FPGA-System-on-Chip (SoC), improves the performance of embedded using

hardware containing more than one type of processor. This approach has shown improved performance, particularly in artificial intelligence (AI), in which computationally demanding models must be trained and executed.

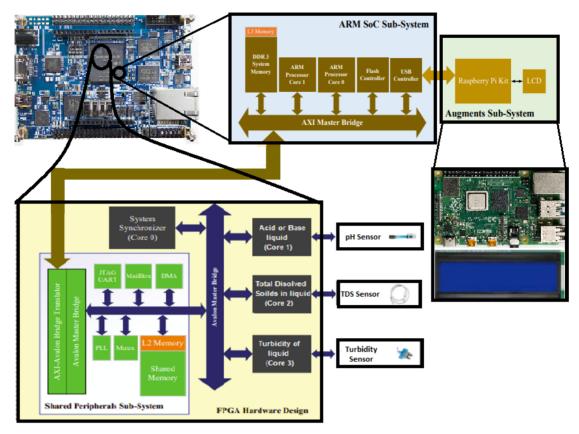

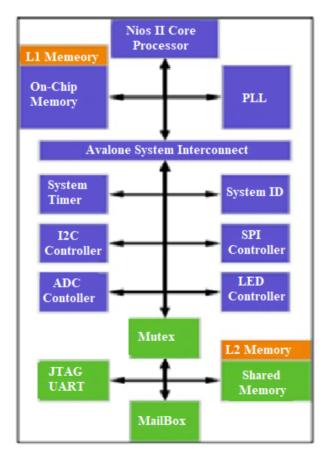

SWQS utilizes different sensors to measure water parameters such as pH, turbidity, and Total Dissolved Solids (TDS) and then processes the data on FPGA-SoC. The proposed design methodology reduces the complexity of the FPGA-SoC heterogeneous platform by adding a middleware layer for software developers to interact with the FPGA system in the form of an application program interface. Therefore, heterogeneous architecture is the best choice for complex systems with multiple input and output ports to enhance the overall system performance.

#### **1.3 PROBLEM STATEMENT**

Currently, in Malaysia, water quality monitoring is done by traditional methods, consisting of taking samples from the area under test and then driving them back to a laboratory to analyze them. The analysis usually is for detecting chemicals and microbial that cause the water's pollution. This method is not only time-consuming but requires significant human interaction. As a result, important data may be lost because of the manual collection process. In addition, the water quality analysis is not done within a short time, so determining a real-time water condition is not plausible. This traditional method is only good if the samples are taken and analyzed simultaneously (Geetha & Gouthami, 2016). Moreover, the water might get contaminated, making it very difficult and costly to recover (Billah, Yusof, Kadir, Ali, & Ahmad, 2019). Moreover, the technicians cannot take samples from all locations, which may lead to inaccurate data (Lezzar, Benmerzoug, & Kitouni, 2020). Besides the issues arising from the manual sample collection, the chemical materials used in water quality testing are usually toxic and very expensive (Khatri, Gupta, & Gupta, 2020).

Even though the research on water quality monitoring systems have been applied many times, the current system is still expensive, has short-distance data transmission, and is not easy to use (Geetha & Gouthami, 2016). Most current SWQS is costly (Pasika & Gandla, 2020), and there should be a big effort by researchers to reduce the cost to make the system more affordable for everyone. Performance is also an important issue

that needs to be considered. SWQS must have high performance and accuracy to reduce errors that might cause poor health conditions and death for the people who consumed the water if the measurements are incorrect.

While FPGA has high processing power, developing an FPGA can be complex and requires more effort than configuring the same design on the Central Processing Unit (CPU) (Besta, Stanojevic, Licht, Ben-Nun, & Hoefler, 2019). In addition, it provides less specialized components (i.e., floating point) operations. It is for this reason that FPGA remains to be a prototype platform for embedded systems. That said, the use of heterogeneous platforms mesh with FPGA has recently gained popularity for design applications that need performance and programmability offered via a processor and flexibility and configurability accomplished using the FPGA fabric (Zhong, Niar, Prakash, & Mitra, 2016). The SoC heterogeneous platforms improve the performance of embedded systems using a hardware design that contains more than one processor.

In addition, when comparing FPGA with other processors such as Arduino and Raspberry Pi, in terms of configurability and implementation, FPGA is reconfigurable based on the user's requirements. However, Arduino and Raspberry Pi are configured and implemented during manufacturing. Additionally, FPGA can process the data in parallel to overcome the latency issue when many inputs are used. On the other hand, there is no way to perform pipelines using processors such as Arduino and Raspberry Pi. In addition, the processing rate of the SWQ data using an FPGA processor is high as its frequency reaches 1 GHz. However, the frequency is slightly lower in other processors, for instance, 16 MHz and 400 MHz for Arduino and Raspberry Pi, respectively. Last but not least, the pins of FPGA are 40 pins that are not hardcoded as their interface can be modified based on the sensor's data exchange protocol, unlike the pins of Arduino and Raspberry Pi, which are hardcoded during the manufacturing process. Moreover, FPGA-SoC is a heterogeneous platform that can work with shared memory for more cooperativity and efficiency. In addition, a heterogeneous platform such as FPGA-SoC improves the performance of embedded using more than one processor.

For these reasons, the main objective of this project is to design SWQS using an FPGA-SoC platform to monitor different water parameters, namely; pH, TDS, and turbidity parameters, rather than relying on the conventional way of measuring water quality parameters.

#### **1.4 RESEARCH OBJECTIVES**

The main objectives of the project are as below:

- To design a reconfigurable hardware-based Smart Water Quality System (SWQS) via using a Field Programmable Gate Array-System-on-Chip (FPGA-SoC) heterogeneous platform.

- To implement a real-time prototype for the proposed Smart Water Quality System (SWQS).

- iii. To evaluate the proposed Smart Water Quality System (SWQS) based on pH, Total Dissolved Solids (TDS), and turbidity parameters.

#### **1.5 RESEARCH SCOPE**

The scope of this research mainly concentrates only on the hardware design of SWQS by utilizing the heterogeneous platform of FPGA-SoC to process signals obtained from water quality sensors. The system design integrates FPGA with the SoC to create a customizable heterogeneous platform that segments the system functionality into tasks. The proposed design in this study will utilize two development kits, the DE10 Nano FPGA-SoC development kit from Intel and the Raspberry Pi development board. The utilized boards will not impact the proposed system design since the design flow is the same for any FPGA development board. The system has two SoC sub-systems: an external one (Raspberry Pi) and an internal one (ARM SoC). The external sub-system will provide the system with all the required augments to ease prototype implementation, like LCD, mouse, and keyboard. The internal SoC will be part of the SWQS as the main system processor.

In addition, testing the proposed system will only be based on three water quality parameters to verify and validate the functionality and reliability of the proposed FPGA-SoC platforms. The utilized sensors in this design will be the pH, TDS, and turbidity sensors. These sensors were used as a proof-of-concept to validate the system's functionality. However, other sensors related to SWQS can be adapted to any future system based on the user's requirements.

#### **1.6 DISSERTATION LAYOUT**

This dissertation is composed of five chapters; a brief introduction and overview of the research are provided in Chapter 1. In Chapter 2, an in-depth investigation was conducted about the previous studies in the SWQS development field. Chapter 3 elaborates on the proposed system, and the design steps needed to develop an SWQS hardware design based on a heterogeneous platform are presented as well as presenting the flow of software to program the system. Furthermore, the proposed system test results and the collected data, were discussed in Chapter 4. Finally, in Chapter 5, the summary of the research findings, contribution, claims, and comparative analysis was reported.

#### **1.7 SUMMARY**

This chapter presented a detailed overview of the research topic, known as SWQS. First, the problem statement of this study was illustrated. Then, the research objectives are presented in this chapter. Furthermore, the scope was explained. Finally, the thesis layout and the relation between each chapter were discussed.

### **CHAPTER TWO**

### LITERATURE REVIEW

#### **2.1 OVERVIEW**

This chapter describes the academic literature correlated with Smart Water Quality System (SWQS) hardware implementation. The main objective of this chapter is to find out and elaborate on the latest research achievements in the field of SWQS design and development. In addition, this chapter highlighted the drawbacks and problems encountered by researchers in their designs, as well as obstacles in providing suitable SWQS solutions.

In Section 2.2, a brief overview of water quality approaches is presented. Then, Section 2.3 explains some sensors that measure water quality parameters such as pH, temperature, turbidity, electrical conductivity (EC), and dissolved oxygen (DO). In Section 2.4, previous studies have been presented based on the controller or the processor. They have been used to collect data on water quality parameters and summarize the related studies' motivations and drawbacks. Section 2.5, on the other hand, shows the proposed SWQS FGPA-based followed by Section 2.6. It presents general information about FPGA in terms of architecture, such as memory, speed, interfaces, etc., and software tools, such as Quartus, Platform Designer, etc. Finally, Section 2.7 summarizes this chapter.

#### 2.2 DIFFERENT WATER QUALITY APPROACHES

There are two ways of measuring water quality. The first is the traditional method involving samples from the river, lake, or any water source, while the second uses sensors to measure water quality. In the following subsections, both conventional and Internet of Things (IoT) methods will be discussed in detail.

#### **2.2.1 Conventional Approach**

The traditional way of measuring water quality parameters, such as the water pH, turbidity, DO, and EC, starts with several samples for testing. Note that sampling selects a small portion of the water to be handled and transported to the laboratory (Ngom, Diallo, Gueye, & Marilleau, 2019). After transporting the samples to the laboratory, specific materials or solutions must be added to measure a specific parameter. For example, to measure the level of phosphorus, one of the crucial water parameters, samples must be transferred to the lab as soon as possible to minimize any external effects that might change the measurement of the total phosphorus. Potassium persulfate should be mixed with the water sample before heating it for 30 minutes. After the heating process, the mixture must be cooled to room temperature. Before measuring the total phosphorus, sodium hydroxide is added and mixed with the sample gently. The last step is to measure the total phosphorus using a spectrophotometer device 7 minutes after mixing. Sometimes, the process can take more than five working days (Li, Jaafar, & Ramli, 2018).

Besides the elaborated identification process, the sampling process is not easy as the samples must be taken from the specified location and involve a highly complex process. Additionally, water samples should be transferred to the laboratory and tested as soon as possible to avoid water pollution. Moreover, this method is time-consuming and costly, requiring equipment cleaning, measuring procedures, and recording. Finally, due to human interaction, many errors might occur during the process, and that will affect the accuracy of the reading.

To conclude, this method is inefficient, and more research should be conducted to develop alternative methods to avoid the challenges mentioned above. Figure 2.1 shows an example of measuring water quality using the traditional method.

Figure 2.1 Conventional-Based Water Quality Monitoring Example (Tucsonaz, 2015)

#### 2.2.2 Internet of Things (IoT) Approach

With the advancement in technology, many alternative methods have been designed and developed to measure water quality parameters incorporating the IoT and machine learning to solve the problems of water quality assessment (Geetha & Gouthami, 2016). The IoT involves using a smart sensor connected to a processor to process the data for monitoring. It can also be connected to a communication tool such as Wi-Fi, LoRa, and Bluetooth to send the data remotely to the main station for real-time monitoring. This way, data can be sent from over a few meters to thousands of meters away, depending on the communication tool's capacity.

This method costs less money when compared to the conventional method, as the sensors and controller are comparatively cheap. More importantly, it provides realtime measurement and monitoring to help the user detects any changes immediately.

That said, SWQS needs more exploration since the sensors are expensive with good quality or cheap with bad quality. Furthermore, the sensors need regular maintenance to avoid damage, as the sensors can be poorly affected by the materials in the liquid. In addition, some communication tools can be expensive, and some can only send data at a lower range, making them unsuitable for big water sources. Figure 2.2 shows an example of measuring water quality using the IoT method.

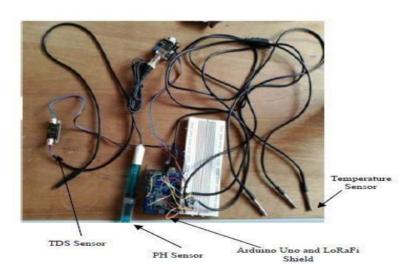

Figure 2.2 IoT-Based Water Quality Monitoring Example Using Arduino (Pinterest, 2017)

#### 2.3 SENSORS USED IN MONITORING WATER QUALITY PARAMETERS

Sensors convert the physical parameter into equivalent measurable electrical quantity, which is given as input to controllers through an optional wireless communication device and parameters.

#### 2.3.1 pH Sensor

The pH represents the number of hydrogen ions in the water. It can be calculated using the negative base of 10 logarithms of the hydrogen ions per liter (Sensorland, 2019). For most water sources, the pH value should be from 6 to 9; if it is more or less, most sea creatures, such as mussels and clams, would be affected negatively (Kraxner, 2015).

pH probe, as shown in Figure 2.3, contains inner and outer tubes. The outer tube contains a Potassium Chloride (KCl) solution, which considers the controller, while the inner tube has a buffer solution with pH 7. The bottom of the inner tube is usually made of a glass overlay that allows the hydrogen ions to move between the probe and test solution. The inner and outer tubes have a silver wire covered with silver chloride connected to the sensor amplifier circuit. Once the probe is placed in the water, the glass membrane will allow the hydrogen ions to go through it and replace the wire's ions which will allow current to flow, causing EC. Figure 2.3 shows the configuration of the pH probe. The voltage values will vary according to pH value; for example, 0 to 0.4 V is equivalent to pH 7 to pH 0, and so on. The pH value will then be obtained when the microprocessor processes the value. If the water or the solution pH is less than 7, this

means a high concentration of hydrogen ions, implying it is an acidic solution. Once the pH value reaches more than 7, the solution is a base. As the pH values might be minimal and unreadable, an amplifier circuit must be added to obtain clear pH values ("PH Meter," 2022).

Figure 2.3 Configuration of pH Probe (Aaruththiran, Yujia, & Bagherian, 2019)

#### 2.3.2 Temperature Sensor

The temperature sensor is made of a probe and built-in Integrated Circuit (IC) containing a register and alarm that will show a warning when the temperature is high or not in the range. A pull-up resistor is used so the microcontroller will reduce the resistance when the sensor sends the data. This sensor can function without additional power as it has a capacitor that stores energy from high signals. However, an external power source is needed to prevent any outbreak of the sensor. The temperature sensor is essential as it affects the conductivity and turbidity as the ions move in the water when the temperature is high (Thermometer, 2019). Figure 2.4 shows the configuration of the temperature probe.

Figure 2.4 Configuration of Temperature Probe (Dhaker, 2020)

### 2.3.3 Turbidity Sensor

Turbidity is the measuring of water clarity and cloudiness. It indicates whether the water has suspended particles or not. It is an important factor that should be measured in most water treatment and supply stations as it might cause harm to aquatic life, not to mention human health.

The concept of a turbidity sensor is a light-transmitting and scattering rate that relies on the total amount of particles in the water. If the light is sent to the water and scattered, the water has many particles that cause the light to scatter. On the other hand, if the phototransistor receives the light, then the water is clear. A phototransistor is connected to a resistor; when the voltage is high, the water is clear of particles ("Gravity: Analog Turbidity Sensor For Arduino," n.d.). Figure 2.5 shows a turbidity sensor.

Figure 2.5 Turbidity Sensor

#### 2.3.4 Conductivity Sensor

The ability of water to allow current through it is known as EC. Current relies on the number of electrons that conduct electricity. The parameters that can affect the conductivity are the solution temperature and ions concentration, as well as the EC parameter, which can affect other parameters such as DO (Acmasindia, 2019). In the conductivity sensor, two electrodes are placed against each other. Once a current is applied to the outer pair, the inner pair potential can be measured. As a result, the current will switch charge electrodes, finally leading the ions to pull the oppositely charged electrodes. As a result, the electrode will carry many charges proportional to the water conductivity ("EC/TDS/PPM Meter On Limited Budget," 2008). An EC sensor is used in various applications such as cooling tower water treatment, boiler water treatment and reverse osmosis monitoring. The sensor selection is based on the required application to ensure lifetime and accuracy. It is measured in "mS" (milliSiemens) or "µS" (microSiemens) per centimeter ("Gravity: Analog Turbidity Sensor For Arduino," n.d.). Depreciating or appreciating water conductivity may indicate that the water is polluted, as some materials might increase conductivity, such as chloride, nitrite, and phosphate ions (O'Donnell, 2017). Not to mention, the conductivity can be proportionally increased when the temperature is high. However, the conductivity sensor suffers from some practical drawbacks. For example, the user cannot determine what ions are dissolved in the water, and the sensor should be cleaned properly before using it again in another solution. Figure 2.6 shows an EC sensor.

Figure 2.6 Electrical Conductivity Sensor

### 2.3.5 Dissolved Oxygen Sensor

DO is an instrumental water parameter that is measured in mg/l. Electrolysis and optics are the methods that are used to measure DO. However, the optic method is better in terms of accuracy and time. The DO sensor consists of a photodetector, two blue and red LEDs, and a luminescent dye between the LEDs, as shown below in Figure 2.7. Once the blue light reaches the dye, the electrons will get energy and let the light emit until it becomes stable. On the other hand, the photodetector will receive the light and destroy it if the solution contains oxygen because there is an interaction between the dye and the oxygen.

Figure 2.7 Dissolved Oxygen Optical Sensor (Staff, 2020)

#### 2.3.6 Total Dissolved Solids (TDS) Sensor

It is a smart sensor that measures the total dissolved materials in a liquid such as water. The Total Dissolved Solids (TDS) sensor measures the solution conductivity as solids that are ionized in liquid-like minerals and salt raise the conductivity of the liquids. Therefore, the TDS sensor mainly measures conductivity; the TDS value could be estimated from these readings. The unit that measured the values is Parts Per Million (PPM). In addition, the sensor's cost starts at \$10 only, but with limited features. For instance, a basic one can measure only the TDS of a liquid. However, expensive one can measure the temperature, salinity, and even more.

It is essential to measure the TDS value, as it indicates that the water has many dissolved solids when the value is high. As time pass, these materials might cause damage and decrease the devices' and water pipelines' lifetime. Therefore, it is important to find a way to solve this issue, like using a water filter (Aquasana, 2022). Figure 2.8 presents an example of a TDS sensor.

Figure 2.8 Total Dissolved Solids Sensor

#### 2.3.7 Free Chlorine Sensor

Free chlorine is one of the most important water quality parameters that need to be measured to ensure water quality. Free chlorine is known as Residual Chlorine (RC). It shows the indication for the water potability level. It measures the amount of RC, which

exists in the liquid as dissolved gas, such as Chlorine (Cl<sub>2</sub>) and hypochlorite ion (ClO–), which might measure hypochlorous acid (HOCl) as well. Free chlorine sensor could be utilized to measure the total amount of three materials Cl<sub>2</sub>, OCl–, and HOCl. Note that Mg/L is the unit that is used to measure the free Cl<sub>2</sub> parameter.

Cl<sub>2</sub> is commonly used to disinfect and clean the contaminated water source. Free Cl<sub>2</sub> in the water can be tested using a different kit, such as digital colorimeters or colorwheel test kits. The sensor read indicates that the water containing free Cl<sub>2</sub> is free of contamination. Figure 2.9 shows an example of a free Cl<sub>2</sub> sensor (Karak, Bhagat, & Bhattacharyya, 2012).

Figure 2.9 Free Chlorine Sensor (Karak et al., 2012).

#### 2.3.8 Water Level Sensor

The water level is an essential parameter that needs to be measured in real-time so fast action can be taken before something happens. A water quality sensor is a device that is utilized to measure the low and high levels of water in a calm situation. The water level sensor is a contact sensor that is used to convert the water level, which is an analog read, into an electrical signal that a microcontroller can process. Different kinds of sensors could be used to measure the water level, such as optical water level sensor, magnetic flap level, hydrostatic level transmitter, ultrasonic sensor, etc.

The water level can be measured by placing the sensor into the liquid at the surface, and then the pressure of the liquid will be converted into the height of the liquid using the following equation:

$$P = \rho. g. H + Po, \qquad (2.1)$$

where P is the pressure of water measured at the surface,  $\rho$  is a fixed value which is the density of the water, g is the gravity, Po is the pressure of the atmosphere at the surface of the liquid, and finally, H is the depth where the sensor was placed. Figure 2.10 shows the ultrasonic sensor, one of the sensors that can be used to measure the water level ("Ultrasonic Level Sensor," 2022).

Figure 2.10 Ultrasonic Level Sensor for Liquids

### 2.4 RELATED RESEARCH

#### 2.4.1 Arduino as a Processing Platform

Arduino is an electronic device that utilizes an open-source platform based on easy-touse hardware and software. Arduino microcontroller could be used to process data from different sensors and devices by sending a set of programming codes to the board. Arduino Software (IDE) is an easy-to-use software that the programmer can use to control the Arduino board. The board has sixteen digital pins and six analog pins, all hard-coded. In addition, Arduino has a built-in clock frequency that reaches up to 16 MHz. Arduino board has been used in many water quality systems with different sensors. The below graphs conclude some of the studies that have used Arduino to design water quality systems ("What Is Arduino?," 2018). In (Ngom et al., 2019), the author presents a water quality monitoring system that uses the LoRa transmission system to send the data to be visible on a website. The system used an Arduino Mega 2560 microcontroller to get and process the sensors' data. Water quality was monitored using four sensors: pH sensor, oxidation/reduction potential (ORP) sensor, EC sensor, and water temperature sensor. Moreover, the Arduino microcontroller was used because it was easy to handle due to the hardware and software flexibility. In addition, the LoRa transmission system transmits the signals using industrial, scientific, and medical (ISM) bands. Therefore, there is no need to pay for the local telecommunication operator. The prototype is a low-power consumption system as all sensors may operate using 5 V, and it is recharged using a solar panel. However, this system did not measure other important water parameters such as water level, turbidity, etc. In addition, the LoRa transmission system is the low range, transmitting data within 2 km to 3 km at a high price because it needs a gateway for transmission. The complexity and cost are the main problems in water quality monitoring system.

Figure 2.11 Overall Water Quality Monitoring System (Ngom et al., 2019)

Moreover, (Li et al., 2018) have designed a wireless water quality system to measure water quality parameters, send it through Wireless Sensor Network (WSN) technology, and finally display the obtained data on a website platform. Arduino Uno microprocessor is used to process the obtained data from the smart sensors and direct the data into the transmission unit to transmit the data. The pH sensor, temperature sensor, and TDS sensor are connected to the processor. TDS is a water quality parameter

used to show the inorganic salts and small amounts of organic matter present in solution in water. The obtained data is transferred to the IoT platform through a Wi-Fi shield. Then, the data will be stored and displayed on the screen using ThingSpeaker software, providing immediate visualization of data simultaneously to ensure that the transmission is done successfully without any loss. A Wi-Fi shield is used as it can transmit a high amount of data, and the transmission rate of a Wi-Fi shield is high compared to other communication mediums. The pH sensors used in this project can function in temperatures between 0 to 60°C without damage within the same range of temperature needed. In addition, this sensor is used to measure the pH value without delay. Furthermore, the TDS sensor has very high accuracy and is waterproof to be used in water. On the other hand, the above system requires calibration before collecting the data. Therefore, data transmission might delay or even lost with a poor Wi-Fi connection. Figure 2.12 presents the prototype of a water quality monitoring system.

Figure 2.12 Prototype of Water Quality Monitoring System (Li et al., 2018)

Additionally, (Chowdury et al., 2019) have developed SWQS to measure the quality of the water remotely. Conductivity, pH, temperature, and turbidity are the parameters that were measured in this project, as seen in Figure 2.13. Arduino Mega 2560 was used to be the processing unit for the data obtained from the sensors because it has several ports, which make it suitable for many sensors to be connected and then display the results on LCD to monitor the data in real-time. The obtained data is just a number; the user might not understand it, which is why a classification method was

required to classify the data of each sensor into good or bad along with the real-time numbers. Thus, big data analytics was integrated with IoT because of its high speed, reliability, and scalability. IoT application was utilized to help the user get the visualized data on a mobile, laptop, and Personal Computer (PC), easing the visualization. Users can get daily/monthly/ even yearly reports as the system has a data management layer to provide the client with the reports. The designer had utilized an Arduino board limited to the interfaces, such as Inter-Integrated Circuit (I2C) and Serial Peripheral Interface (SPI), even Arduino Mega has many pins, but still, the interfaces cannot be changed as it is hard-coded and cannot be reconfigured.

Figure 2.13 Overall Water Quality Scheme (Chowdury et al., 2019)

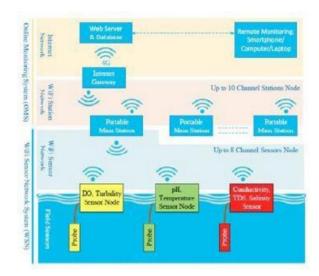

Moreover, (Lezzar et al., 2020) have designed and developed an IoT system that measures specific water quality parameters to achieve high accuracy. The system has five sensors to measure parameters that indicate if the water is contaminated with pH, temperature, turbidity, ORP, and Cl<sub>2</sub>. ORP is an essential environmental water parameter that reflects the clearness of the liquid and could remove the pollutants in ponds. Meanwhile, the Cl<sub>2</sub> sensor measures the Cl<sub>2</sub> concentration in the water, which needs to be kept at a low level to keep drinking water healthy. The Arduino ATmega1281 microcontroller is the main processing unit to which all sensors are connected. The system solves the problem of the power supplies as it is attached to solar cells to recharge the batteries. All obtained data was sent to the user and stakeholders using the Message Queuing Telemetry Transport (MQTT) protocol via the SIM800c module to achieve quick data transfer. The system can monitor the water quality in a fixed tank or mobile water source. Moreover, it can localize where the water is contaminated exactly. Thus, a decision can be made accordingly. The designed system consists of a cloud infrastructure to get the parameters remotely. It is a lifespan system that was designed to avoid short-term maintenance. SIM800c module is a GSM/GPRS solution that supports different frequency bands instead of Wi-Fi because Wi-Fi is unavailable everywhere. Figure 2.14 presents the overall system architecture.

Figure 2.14 Overall System Architecture (Lezzar et al., 2020)

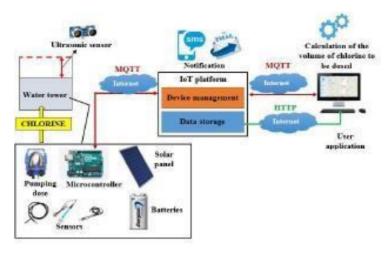

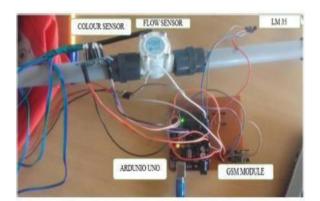

Additionally, (Saravanan, Anusuya, Kumar, & Son, 2018) have proposed a Supervisory Control and Data Acquisition (SCADA) system that cooperates with IoT for real-time water quality monitoring in India. Several sensors measure physical and chemical water parameters such as water temperature, flow, pressure, pH, and color. A color sensor is utilized to discover whether the water is contaminated. When the water is mixed with dust, it will be shown in the RGB value within the range of 0 - 255. GPRS module was connected to Arduino ATmega 368 microcontroller to connect the latter with the internet. The water contamination status was sent to the server through a personal computer or mobile device to be displayed on the website. The data obtained from the sensors were viewed on the web platform, and there was an LCD for viewing data on-site.

Moreover, after the data was obtained from each sensor, it was compared with the threshold values to inform authorized users via SMS of any abnormal sensing to take action needed as fast as possible. SCADA system was used to get the sensor reading from different stations for real-time monitoring. In addition, the primary advantage of the SCADA system is the report generation available to the operator in each station. The system is designed to make the operation easier, reduce size, weight, and cost, and improve sensitivity. Using the General Packet Radio Services (GPRS) module has many advantages, such as high-speed communication between a mobile device and the main network. Arduino microprocessor is used instead of a Programmable Logic Controller (PLC) controller to accelerate the SCADA system speed. Furthermore, the most exciting systems were standalone devices that were not connected to any IoT platform, while this system utilized IoT to avoid taking the results on-site. However, the proposed SCADA system cannot be implemented in areas not covered by Wi-Fi; hence, the GPRS module constantly needs Wi-Fi. Figure 2.15 shows hardware implementation for water quality monitoring devices in the pipeline.

Figure 2.15 Hardware Implementation for Water Quality Monitoring Device in Pipeline (Saravanan et al., 2018)

An IoT system was designed by (Mukta, Islam, Barman, Reza, & Khan, 2019) to measure four different parameters: pH, conductivity, temperature, and turbidity. Arduino Uno is used as a microcontroller to process the data obtained from the sensors. The Arduino microcontroller is connected to a desktop directly, so the obtained data can be displayed on it. An application was developed in the .NET platform to check the obtained data with the World Health Organization (WHO). The sixty-water sample was taken from three sources: drinkable, unclear, and natural. Fast forest binary classifiers are machine learning algorithms for training and testing the module, which has been used to classify whether the test water sample is drinkable or not. In the end, it was

concluded that the fast forest algorithm is the best in terms of accuracy, and the F1 score, which measures the model's accuracy, was used for the overall system performance. In addition, the system is not real-time based, meaning samples need to be collected, which is time-consuming. Apart from that, some water features might be affected when transferring it. Additionally, Figure 2.16 illustrates the experimental setup of the SQWM system.

Figure 2.16 Experimental Setup of SQWM System (Mukta, Islam, Barman, Reza, & Khan, 2019)

Furthermore, (Pujar, Kenchannavar, Kulkarni, & Kulkarni, 2020) have developed a real-time water quality system to monitor six water parameters like pH, EC, nitrate, Biochemical Oxygen Demand (BOD), Total Dissolved Oxygen (TDO), and temperature. The sensors are connected to Arduino Mega 2560 controller to process the sensors' data, as shown in Figure 2.17. A total of thirty-six (36) samples were randomly collected from six different stations. Note that the samples were taken in different seasons throughout the year to check whether the weather impacts water quality or not. After data obtaining, it was sent through the ESP8266 Wi-Fi shield to the main station for monitoring. One-way and two-way Analysis of Variance (ANOVA) analysis tools were used to evaluate the system, and it has been found that one-way ANOVA is the most suitable tool for training data, such as an IoT system. Furthermore, this research found that different seasons have different results. In other words, temperature, DO, conductivity, BOD, and nitrate parameters were impacted in the winter.

Figure 2.17 Circuit and Block Diagram of IoT System (Pujar et al., 2020)

(Encinas, Ruiz, Cortez, & Espinoza, 2017) proposed a real-time water quality system to monitor three water quality parameters, namely pH, temperature, and DO. Arduino microcontroller was implemented for processing the data into Zigbee wireless communication tool for transmitting the data obtained from the sensor remotely to the main station. An application was developed using the C# programming language, in which its database was designed using the MySQL platform. While the readings were obtained from the sensor, it was directly sent to the database for local storing and sent to a web server to visualize the data on the application. The overall system costs less compared to other designs, and it is portable and has low power consumption.

Additionally, the C# programming language was used because it allows giving a request to the sensors to send their readings through the microcontroller along with a multiplexer. The Zigbee tool will transmit the data obtained from the sensors to the computer for display on the application. A multiplexer is a device that is used to raise the efficiency of the communication system by collecting the data from each sensor and transmitting via a single line only. However, the system was designed to display data without alerting the end user if the water condition was bad. Developing an artificial intelligence (AI) module to alert when the data is not within the standards set in the database has been recommended. Figure 2.18 presents the system's general blocks and data flow.

Figure 2.18 System General Blocks and Data Flow (Encinas et al., 2017)

### 2.4.2 Raspberry Pi as Processing Platform

The Raspberry Pi is another low-cost and small-size controller that could function as a computer along with other peripheral devices, such as a mouse and keyboard. It helps developer to design any device using Python or Scratch programming languages. Note that Raspberry Pi has the capability of being connected to other devices, such as sensors. Since the Raspberry Pi controller has been used in many smart devices to process the sensors' data, it has an inbuilt Wi-Fi module for remote access. Thus, there is no need for external equipment. In addition, the Raspberry Pi controller can function on 12 V only; thus, it can be implemented easily. Many water quality systems have utilized the Raspberry Pi controller to collect the data from water quality sensors and send it through different transmission devices for monitoring ("What Is a Raspberry Pi?," 2015). The below studies show the main advantages and disadvantages of using Raspberry Pi in water quality designs.

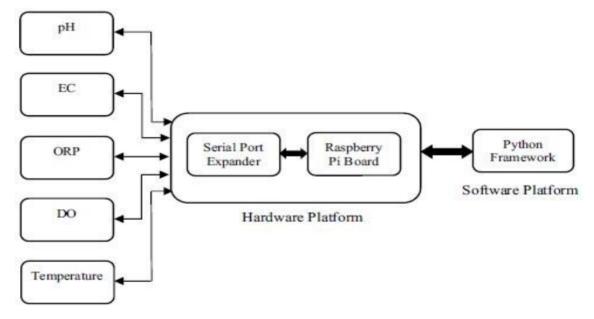

(Khatri et al., 2020) invented a real-time water quality system in India that measures water quality parameters using different sensors, such as pH sensor, EC sensor, ORP sensor, DO sensor, and temperature sensor, as mentioned in Figure 2.19. ORP is a water quality measurement that indicates if the water is oxidizing or reducing. ORP parameter should be measured when its value is low, indicating that the water has less DO. It then leads to an increase in the toxicity of certain materials, which increases water contamination. The obtained data from the sensor was processed using a Raspberry Pi 3 controller, which collects data, analyzes it, and makes decisions since the controller is programmed using python. Finally, the system's performance was validated by comparing the results with another work using Absolute Percentage Relative Error (APRE). Raspberry Pi has an inbuilt Wi-Fi module for remote access. Thus, there is no need for external equipment. In addition, the Raspberry Pi controller can function on 12 V only; therefore, it can be implemented easily. The system has very high accuracy in measuring the parameters compared to other work. However, Linux operating systems must be used when implementing a system using Raspberry Pi, which is not popular among users. In the future, it has been recommended to implement a water quality monitoring system using fuzzy logic in the IoT environment and distribution networks.

Figure 2.19 Block Diagram of Developed (Khatri et al., 2020)

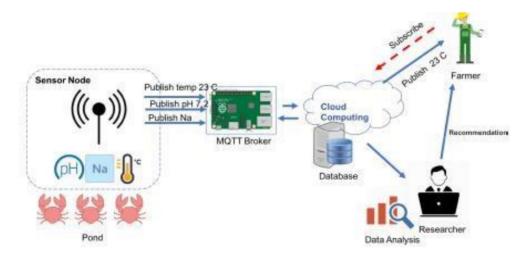

(Niswar et al., 2018) proposed a water quality monitoring system using an IoT platform to measure water quality for crab farming in Indonesia. The system has three sensors to measure pH level, temperature, and salinity. The sensors are connected to Raspberry Pi and Arduino processors for processing the data into the mobile phone using the MQTT protocol. LoRa wireless communication system is the middle way to transfer data long distances. The user has designed a web-based application for the

mobile phone to remotely monitor water quality using the node-red platform. This opensource programming tool can be used to communicate with IoT devices. The system was designed to alert the crab farmer if the farm water quality is not acceptable for all water parameters. The system is essential for crab farmers to monitor the water quality parameters as water quality can affect their survival. However, the system can measure only pH, salinity, and temperature and neglects other parameters such as DO, which might have a bad impact if it is not within the acceptable level. In addition, the LoRa system and the sensors are connected to the Arduino microprocessor and Raspberry Pi, making it complicated. Furthermore, the data was transferred using 3G and 4G networks, which are not available everywhere, which might delay data transfer or cause data loss. The author recommended adding this system to the water circulation to reduce human intervention for improving water quality. In addition, it has been recommended to reduce the energy consumption for all devices used to design the system. Figure 2.20 shows an IoT-based Monitoring System.

Figure 2.20 IoT-based Monitoring System (Niswar et al., 2018)

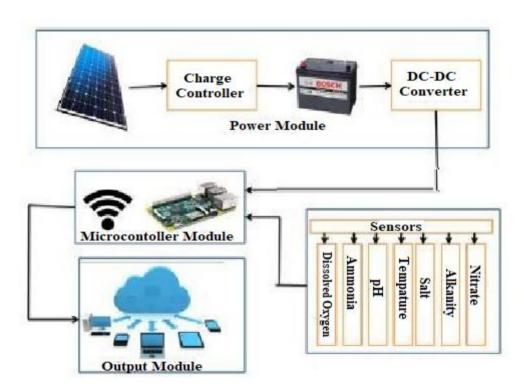

A real-time water quality monitoring system has been proposed for aquaculture farmers to alert them if the water body is polluted (Raju & Varma, 2017). The system consisted of several sensors to measure different water quality parameters. The water quality sensor: DO, temperature, carbonates, nitrate, pH, ammonia, and salt, are connected to a Raspberry Pi 3 controller that contains an inbuilt Wi-Fi module. The system was powered using a solar panel to reduce power consumption. The system always stores data and alerts the farmers if the water conditions are not in the allowable range. In addition, a mobile application was designed to allow the user to monitor the data remotely in real-time so the farmer can view the historically obtained data. Using solar panels will overcome the problem of electricity breakdown as the farmers face a lot of power cuts. When the farmer receives a message alerting him of abnormal water conditions, the message also states how to solve the faced issue. Nevertheless, the overall system's initial cost is high compared to other systems. The cost and energy consumption can be reduced when the system is developed to be automated using an internet network. The system architecture is shown in Figure 2.21.

Figure 2.21 System Architecture (Raju & Varma, 2017)

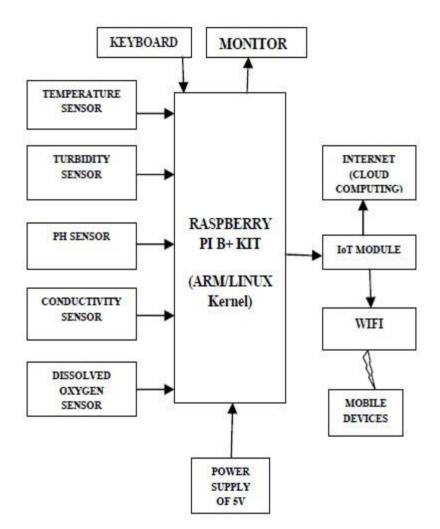

(Vijayakumar & Ramya, 2015) designed a low-cost water quality monitoring system that used smart sensors to measure five water quality parameters; pH, conductivity, turbidity, DO, and temperature. These sensors are connected to a Raspberry Pi B+ controller to process the sensors' data to the USR-WIFI232-X-V4.4 module that transfers the obtained data to the cloud using a gateway. A mobile application was provided to view the data obtained from the sensors. Raspberry Pi controller can be connected to several sensors and interfaces simultaneously, making it

suitable for systems with many inputs and outputs. The controller and the used wireless communication module were the best choice for such a system as it is portable, low cost, and capable of processing, analyzing, sending, and finally viewing data on a mobile phone. Thus, it was more efficient compared to other systems. It has been suggested to measure biological parameters as the system measured only physical parameters and implement the design in many areas to collect more data about the condition of the water body. The overall block diagram is presented in Figure 2.22.

Figure 2.22 Overall Block Diagram (Vijayakumar & Ramya, 2015)

#### 2.4.3 TI CC3200 as Processing Platform

The Texas Instrument CC3200 microcontroller is a single chip with an internal Wi-Fi chip invented for IoT applications. It allows the developer to design a completed application using only a single chip. It contains software, tools, and sample applications

and is easy to program. It has different peripherals, such as I2C, Serial Peripheral Interface (SPI), Universal Asynchronous Receiver-Transmitter (UART), and Analog-to-Digital Converter (ADC) channels ("CC3200 Is the Industry's First Single-Chip Microcontroller Unit with Built-in Wi-Fi," 2015). TI CC3200 has been used to design some water quality to process the data obtained from the sensors.

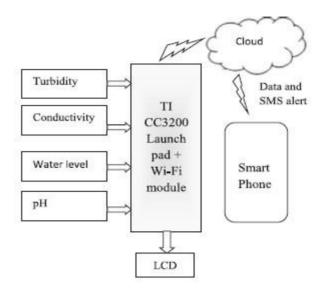

Additionally, (Geetha & Gouthami, 2016) have designed a cheap system for water quality monitoring. To check water quality, the design uses five sensors to measure pH, turbidity, temperature, water level, and EC. The data is collected using a TI CC3200 controller, a single chip with Wi-Fi built into it for wireless communication purposes, as presented in Figure 2.23. The controller, as mentioned above, is programmed to store the data in the cloud using the Ubidots platform to analyze the data after storing it. Testing WHO's data is added to the module to compare it to the obtained data from sensors. In addition, once readings from sensors reach abnormal values, the user will get an alert that a problem needs to be solved. TI CC3200 controller is easy to use, and its speed is high compared to other processors with external Wi-Fi chips (Texas instrument CC3200 Simple Link, 2017). The controller works in four modes; Hibernate, Sleep, Deep Sleep, and Active. Thus, the consumed power will be reduced because the controller is not always functioning. However, using a Wi-Fi module is not a good choice as it consumes high power. Still, its range of communication is high compared to other communication protocols, not to mention the need for external hardware chips that are not needed anymore when using a Wi-Fi module. It has been recommended to improve the system by implementing machine learning algorithms for detecting abnormal water quality parameter values.

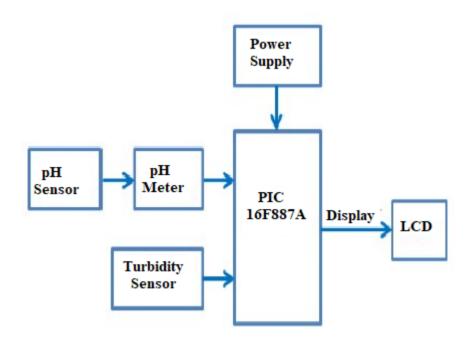

Figure 2.23 Overall Block Diagram (Geetha & Gouthami, 2016)

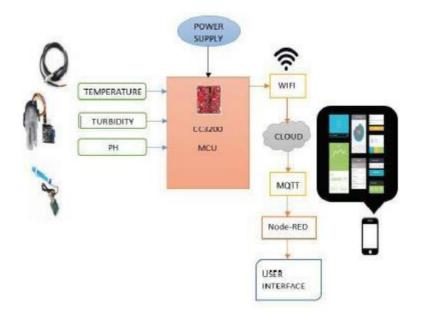

Furthermore, a new system has been developed to monitor the water quality parameters in real-time to reduce human intervention (Billah et al., 2019). This system was designed to allow the farmers to monitor their waterways to take the actions needed when the water parameters are not good. Thus, three sensors were used to measure temperature, pH, and turbidity. TI CC3200 microcontroller is the main chip used to process the data from the sensors and send it through the Wi-Fi network. Finally, the data was displayed on LCD using graphs, charts, etc. Then, data is transmitted using MQTT to the end-user for monitoring purposes. CC3200 microcontroller has built-in Wi-Fi. Hence, there is no need for outer Wi-Fi equipment. Furthermore, the MQTT protocol is used to make the communication between the microprocessor and end-user easier as it is not complicated. However, the MQTT protocol was low in data rate transmission, and that caused the system to be slow. On the other hand, some challenges have been faced during real implementation, such as the turbidity parameters being unstable most of the time as it is susceptible to the water flowing; this sensor needs some time to get a more stable reading. Besides, the turbidity sensor can only measure the quality, not the quantity. Therefore, the user cannot get the turbidity reading like other sensors. Figure 2.24 presents the overall block diagram.

Figure 2.24 Overall Block Diagram (Billah et al., 2019)

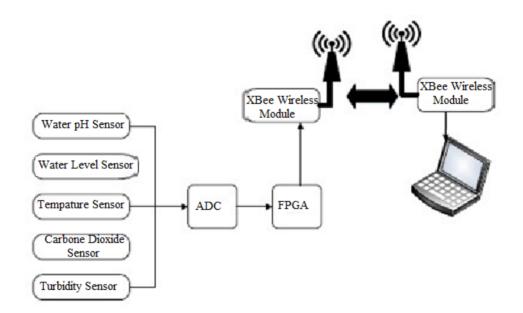

#### 2.4.3.1 FPGA as Processing Platform

FPGA is a reconfigurable device that contains many programmable units (Giesemann et al., 2014). This device is an integrated circuit made of semiconductor material. The main advantage of FPGA is any user can reconfigure the device's electrical functionality as it is not hard-coded. These powerful devices can be customized to accelerate key workloads and enable design engineers to adapt to emerging standards or changing requirements. In Section 2.5, we will elaborate more on the architecture of an FPGA.